2021年02月23日

【VHDL入門】UART 送受信繰り返しのテストベンチ作成してみたい

【VHDL入門】UART 送受信繰り返しのテストベンチ作成してみたい

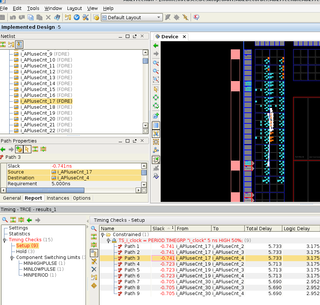

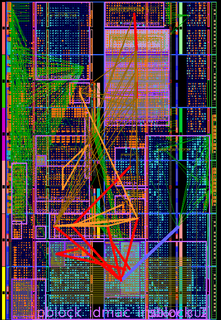

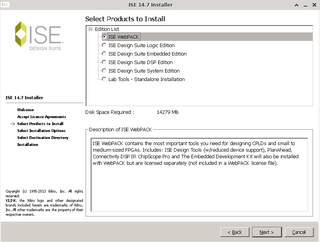

実装後まにあうのか ということでテストです。

実装後というオプションがありますのでそれを使います。

通常のインプリメントができるようにします

シンセシスオプションで optmode は とりあえず speed です。 オプトレベルノーマル

キープ ハイアラキー これやらないと なにがどこにあるのかわからなくなります。

ネットリストの ハイアラキー rebuilt にしておきます。

こんなところかな

あとは デザインペイン なかの ラジオボタン implimentation simulaton のしむを選びます

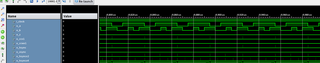

そうしておいて POST ROUTE をえらんで ごーーーーです

ここのところのUART のTX RXですが

実は もともとのの VHDLでは RXのほうが 早く終わってしまいます。

これは は TXが 送信終了 して DONE なのですが RXは最後の STOPビットが 立ち上がった瞬間に 終了するためです したがって 送信終了で 繰り返すことになります。

RXの終了で繰り返すみたいな シミュレーションにしてもいいのですが やっぱこれは 次の受信の準備は早い方がいいので このままです。

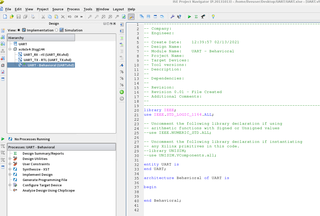

送信終了 での繰り返し込で 実装したいので 最上位のVHDLは次の通りです

オリジナルにはない パリティチェックは いれました。

今日のところは ここまでです。

今日のところは ここまでです。

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; entity UART is generic ( g_CLKS_PER_BIT : integer := 115 ; -- Needs to be set correctly g_bitlittleEndian : std_logic := '0' -- Needs to be set correctly ); port ( i_Clk : in std_logic; i_nRST : in std_logic :='1'; i_TX_stb : in std_logic; i_TX_Byte : in std_logic_vector(7 downto 0); o_TX_Active : out std_logic; o_TX_Serial : out std_logic; o_Parity : out std_logic; o_TX_Done : out std_logic; i_RX_Serial : in std_logic; o_RX_stb : out std_logic; o_Parityerr : out std_logic; o_RX_Byte : out std_logic_vector(7 downto 0) ); end UART; architecture Behavioral of UART is component UART_TX generic ( g_CLKS_PER_BIT : integer := 115 ; -- Needs to be set correctly g_bitlittleEndian : std_logic := '0' -- Needs to be set correctly ); port ( i_Clk : in std_logic; i_TX_stb : in std_logic; i_TX_Byte : in std_logic_vector(7 downto 0); o_TX_Active : out std_logic; o_TX_Serial : out std_logic; o_Parity : out std_logic; o_TX_Done : out std_logic ); end component; signal w_Parity :std_logic; component UART_RX generic ( g_CLKS_PER_BIT : integer := 115 ; -- Needs to be set correctly g_bitlittleEndian : std_logic := '0' -- Needs to be set correctly ); port ( i_Clk : in std_logic; i_nRST : in std_logic :='1'; i_RX_Serial : in std_logic; o_RX_stb : out std_logic; o_Parityerr : out std_logic; o_RX_Byte : out std_logic_vector(7 downto 0) ); end component; type C_SmLoopback is (Idle_st,Run_st,TurnAround_st ); signal SmLoopback : C_SmLoopback := Idle_st; signal Rtxdata : std_logic_vector(7 downto 0); signal Rtx_stb : std_logic; signal wtx_Serial : std_logic; begin UART_TXinst : UART_TX generic map (g_CLKS_PER_BIT) port map (i_Clk, i_TX_stb, i_TX_Byte,o_TX_Active,o_TX_Serial,o_Parity,o_TX_Done); UART_RXinst : UART_RX generic map (g_CLKS_PER_BIT) port map (i_Clk,i_nRST, i_RX_Serial,o_RX_stb,o_Parityerr,o_RX_Byte); end Behavioral;更にこれを シミュレーションします。 オリジナルにない けど i_nRST の非同期 リセットもいれています。 都合の話です。

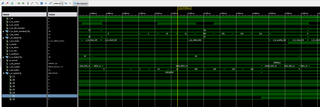

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; entity UARTLoopback is generic ( g_CLKS_PER_BIT : integer := 115 ; -- Needs to be set correctly g_bitlittleEndian : std_logic := '0' -- Needs to be set correctly ); port ( i_Clk : in std_logic; i_nRst : in std_logic; o_TX_stb_monitor : out std_logic; o_TX_Byte_monitor : out std_logic_vector(7 downto 0); o_TX_Active : out std_logic; o_TX_Serial : out std_logic; o_Parity : out std_logic; o_TX_Done : out std_logic; --i_RX_Serial : in std_logic; o_RX_stb : out std_logic; o_Parityerr : out std_logic; o_RX_Byte : out std_logic_vector(7 downto 0) ); end UARTLoopback; architecture Behavioral of UARTLoopback is component UART generic ( g_CLKS_PER_BIT : integer := 115 ; -- Needs to be set correctly g_bitlittleEndian : std_logic := '0' -- Needs to be set correctly ); port ( i_Clk : in std_logic; i_nRst : in std_logic; i_TX_stb : in std_logic; i_TX_Byte : in std_logic_vector(7 downto 0); o_TX_Active : out std_logic; o_TX_Serial : out std_logic; o_Parity : out std_logic; o_TX_Done : out std_logic; i_RX_Serial : in std_logic; o_RX_stb : out std_logic; o_Parityerr : out std_logic; o_RX_Byte : out std_logic_vector(7 downto 0) ); end component; signal w_Parity :std_logic; type C_SmLoopback is (Idle_st,Run_st,TurnAround_st ); signal SmLoopback : C_SmLoopback := Idle_st; signal Rtxdata : std_logic_vector(7 downto 0):=(others =>'0'); signal Rtx_stb : std_logic; signal Rrx_stb : std_logic; signal wTxDone : std_logic; signal wtx_Serial : std_logic; begin UARTinst: UART generic map(g_CLKS_PER_BIT=>g_CLKS_PER_BIT, g_bitlittleEndian=>g_bitlittleEndian ) port map( i_Clk => i_Clk, i_nRst => i_nRst, i_TX_stb=>Rtx_stb, i_TX_Byte=>Rtxdata, o_TX_Active=>o_TX_Active, o_TX_Serial=>wtx_Serial, o_Parity=>o_Parity, o_TX_Done=>wTxDone,--o_TX_Done, i_RX_Serial=>wtx_Serial, o_RX_stb=>Rrx_stb,--o_RX_stb, o_Parityerr=>o_Parityerr, o_RX_Byte=>o_RX_Byte ); o_TX_Byte_monitor<=Rtxdata; o_TX_stb_monitor <=Rtx_stb; o_RX_stb<=Rrx_stb; o_TX_Done<=wTxDone; process (i_Clk,i_nRst) begin if i_nRst='0' then SmLoopback<=Idle_st; elsif rising_edge(i_Clk) then case SmLoopback is when Idle_st => SmLoopback<=Run_st; Rtx_stb<='1'; when Run_st => Rtxdata<=Rtxdata+'1'; Rtx_stb<='0'; SmLoopback<=TurnAround_st; when TurnAround_st => Rtx_stb<='0'; if(wTxDone='1') then SmLoopback<=Idle_st; end if; end case; end if; end process; o_TX_Serial<=wtx_Serial; end Behavioral;いよいよ 実装後のRUNです。 あとであんがつく 彼岸のぼたもちですが 送信のモニタが 2つ進んでいるように見えます。 送ってるのを 出せば良かったかも 送ったら 変化させたのでこんななっちゃいました。 仕方なく 送信中のデータを むりくり表示すると ピッタリです。

今日のところは ここまでです。

今日のところは ここまでです。

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10558780

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック