2021年02月13日

【VHDL入門】最初の扉を叩くのだ。

昨日 Xilinx_ISE_DS_14.7_1015_1 をコピーして ダウンロード 早速洗礼をうけた

あーあ ライブラリがリンクがないらしい まぁいいだろう /usr/lib64 ここの ncurses のライブラリを あれしてなにだ 具体的には ln -s /usr/lib64 を 我がコンピュータは 64ビット版なのでこうだ。

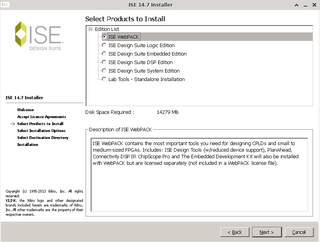

まぁ いいだろう それにしても でかいファイルだ /opt にインストールしたいので root でインストールする。

インストールの間暇なので スペースコブラでもみながらまつ 左腕に銃を持つ男だってさ

スターウォーズみたいな 宇宙人がでてくる。 ブサイクな おっさんヒーロー? だ。

地球人にしては あれでなにな 女性たちも登場する。

ちょっとおしゃべりだ インストールすむまでの・・

具体的なことが重要なので 具体的に 動作済みのソースを WEB上から いただいて それをもとに解説してみる。 やりたいことは すでに動いているIPを 自分のVHDLにつないで動かす シミュレーターをつかう。 この順番 だれのためって 忘れっぽい 自分のためだ。 ははは

数回の 連載?なのだが ほぼこれで フィッターで一時間級の 規模なら 個人でもできるようになるエッセンスは入っているつもりだ。

あと 老婆心なのだがある寺 アルテラ VS ザイリンクス でいうと

アルテラは 配置のマニュアルは有償品の開発ツールでないとできないが ザイリンクスなら WEBパック無償でできる。 これは経験則だが 20MHzを超える設計は 何らかの配置配線が必要なことが多い

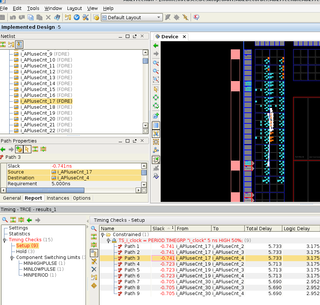

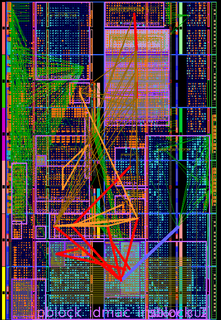

私の経験では FPGAを250Mhzで動作させたとき これを 完全にコンパイラ任せにすると 全く動作しなかった ^^; マニュアルで フロアプランすると 普通に動作した。

アルテラでもやってみようとおもうのだけど 普段の仕事が ご多分にもれず バスの切り替えとか

そんなものが大半だから アルテラでのフリーで事足りる。

私のアルテラ歴では 動作も5MHz とか10Mhz ぐらいでしか組んだことがない ^^; 20Mhz超えた設計なんてしたことがない。^^; クロックついてりゃいいみたいな。

私のザイリンクス歴では 200Mhz超えたものばかり 20Mhzでは許してもらえない^^;ときは フロアプラン無料のザイリンクス一択だ。

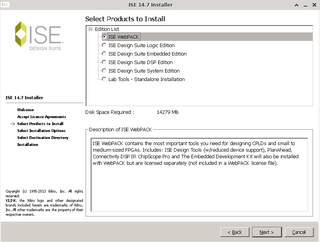

ちょっとVHDLやろうとおもったので ザイリンクスダウンロードしてみよう

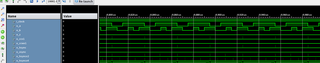

【VHDL入門】UARTを実装してみる。シミュレーターまで

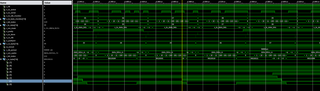

【VHDL入門】20分周のVHDLから シミュレーションまで

分周はいくらかやり方があって カウンター地との比較をしてみた。 本当にカウンターの上位ビットをそのまま出力するのもありだ。 1,2,4,8・・・分周になる。

余談編

【VHDL入門】個人で作った一番でっかいVHDLはコンパイルにえーとざっくり1時間かかるのだ

これは アマチュアレベルではでっかいほうだ、そして250Mhzで動作しているので おきらくとは言い難い。 小さなVHLDソースでは 簡単に250Mhz動作するが 大きくなると うざい。

ちいさなVHLDソースを でっかい FPGAに コンパイラまかせフィットさせると 本当にスピードでませんぜだんな 10Mhz とか 5Mhz とかしか動かん ^^; なんじゃそりゃみたいな

DDR2つかったのだけど あれ面倒くさかった 。

インストールが済んだ

cd opt/Xilinx にはいって セットアップを起動する

/opt/Xilinx/14.7/ISE_DS/ISE/bin/lin64 ここに起動ファイルがあるのでここの iseを起動する。

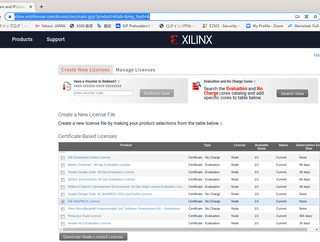

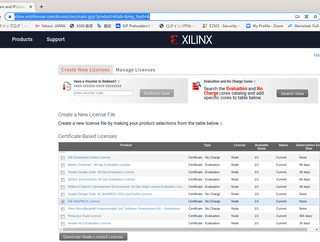

ありゃ ライセンスが いるらしい。

ライセンスファイルが手に入ったので

export XILINXD_LICENSE_FILE=/home/liveuser/.xilinx/

/opt/Xilinx/14.7/ISE_DS/settings64.sh

みたいな 環境変数に ライセンスファイルの置き場を指定 そうすると

起動できます。

これで コンソールから ise エンターで 起動できます。

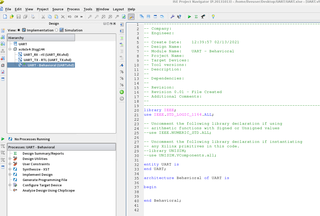

早速起動して uart を いれみます。

https://www.nandland.com/vhdl/modules/module-uart-serial-port-rs232.html

のファイルを あれします。

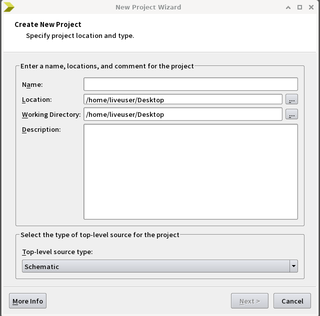

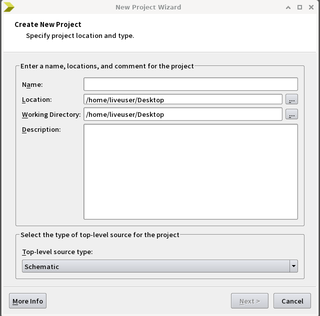

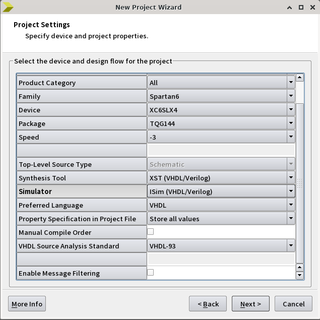

file ー> newproject で

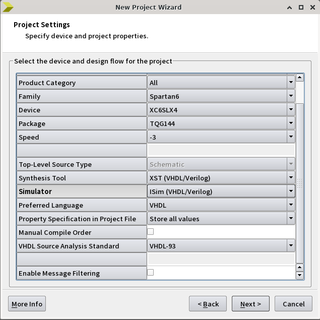

プロジェクト名を 例えば myuart とかいれます。 ここで どのデバイス使うかとか設定ありますが

とりあえず spartan6 ぐらいいれましょうか 一通りいろいろついてますので

モデルシムつかえるのかな? ちょっとわかっていません。追って考えましょう

ファイル追加して VHDLモジュールを つくります。 最初てきとうに

https://www.nandland.com/vhdl/modules/module-uart-serial-port-rs232.html

にあるように 同じ名前でファイルをつくります。 送受信の箱をつくって

そのしたに階層構造で このページのデモをつくってみます。

コンポーネントという形で 下層においていきます。

entiry なんちゃら is

なのですが

componet に is はつきません これ面倒です。

最上位まだ書いていませんが コンポーネントをこんな感じにおいていきます。

[liveuser@localhost Xilinx_ISE_DS_14.7_1015_1]$ ls

Microsoft.VC90.CRT autorun.inf common edk ise lib planahead sysgen xinfo xsetup

Microsoft.VC90.MFC bin data idata labtools msg planahead_wp webpack xinfo.exe xsetup.exe

[liveuser@localhost Xilinx_ISE_DS_14.7_1015_1]$ ./xsetup

/home/liveuser/Downloads/Xilinx_ISE_DS_14.7_1015_1/bin/lin64/_xsetup: error while loading shared libraries: libncurses.so.5: cannot open shared object file: No such file or directory

[liveuser@localhost Xilinx_ISE_DS_14.7_1015_1]$

あーあ ライブラリがリンクがないらしい まぁいいだろう /usr/lib64 ここの ncurses のライブラリを あれしてなにだ 具体的には ln -s /usr/lib64 を 我がコンピュータは 64ビット版なのでこうだ。

$ ls -1 /usr/lib64/libncurses*

/usr/lib/libncurses.so

/usr/lib/libncurses++.so

/usr/lib/libncurses++w.so

/usr/lib/libncursesw.so

/usr/lib/libncurses++w.so.6

/usr/lib/libncursesw.so.6

/usr/lib/libncurses++w.so.6.0

/usr/lib/libncursesw.so.6.0

$ sudo ln -s /usr/lib64/libncursesw.so.6.0 /usr/lib64/libncurses.so.5

$ sudo ln -s /usr/lib64/libncursesw.so.6.0 /usr/lib64/libtinfo.so.5

まぁ いいだろう それにしても でかいファイルだ /opt にインストールしたいので root でインストールする。

インストールの間暇なので スペースコブラでもみながらまつ 左腕に銃を持つ男だってさ

スターウォーズみたいな 宇宙人がでてくる。 ブサイクな おっさんヒーロー? だ。

地球人にしては あれでなにな 女性たちも登場する。

ちょっとおしゃべりだ インストールすむまでの・・

具体的なことが重要なので 具体的に 動作済みのソースを WEB上から いただいて それをもとに解説してみる。 やりたいことは すでに動いているIPを 自分のVHDLにつないで動かす シミュレーターをつかう。 この順番 だれのためって 忘れっぽい 自分のためだ。 ははは

数回の 連載?なのだが ほぼこれで フィッターで一時間級の 規模なら 個人でもできるようになるエッセンスは入っているつもりだ。

あと 老婆心なのだが

アルテラは 配置のマニュアルは有償品の開発ツールでないとできないが ザイリンクスなら WEBパック無償でできる。 これは経験則だが 20MHzを超える設計は 何らかの配置配線が必要なことが多い

私の経験では FPGAを250Mhzで動作させたとき これを 完全にコンパイラ任せにすると 全く動作しなかった ^^; マニュアルで フロアプランすると 普通に動作した。

アルテラでもやってみようとおもうのだけど 普段の仕事が ご多分にもれず バスの切り替えとか

そんなものが大半だから アルテラでのフリーで事足りる。

私のアルテラ歴では 動作も5MHz とか10Mhz ぐらいでしか組んだことがない ^^; 20Mhz超えた設計なんてしたことがない。^^; クロックついてりゃいいみたいな。

私のザイリンクス歴では 200Mhz超えたものばかり 20Mhzでは許してもらえない^^;ときは フロアプラン無料のザイリンクス一択だ。

ちょっとVHDLやろうとおもったので ザイリンクスダウンロードしてみよう

【VHDL入門】UARTを実装してみる。シミュレーターまで

【VHDL入門】20分周のVHDLから シミュレーションまで

分周はいくらかやり方があって カウンター地との比較をしてみた。 本当にカウンターの上位ビットをそのまま出力するのもありだ。 1,2,4,8・・・分周になる。

余談編

【VHDL入門】個人で作った一番でっかいVHDLはコンパイルにえーとざっくり1時間かかるのだ

これは アマチュアレベルではでっかいほうだ、そして250Mhzで動作しているので おきらくとは言い難い。 小さなVHLDソースでは 簡単に250Mhz動作するが 大きくなると うざい。

ちいさなVHLDソースを でっかい FPGAに コンパイラまかせフィットさせると 本当にスピードでませんぜだんな 10Mhz とか 5Mhz とかしか動かん ^^; なんじゃそりゃみたいな

DDR2つかったのだけど あれ面倒くさかった 。

インストールが済んだ

cd opt/Xilinx にはいって セットアップを起動する

/opt/Xilinx/14.7/ISE_DS/ISE/bin/lin64 ここに起動ファイルがあるのでここの iseを起動する。

ありゃ ライセンスが いるらしい。

ライセンスファイルが手に入ったので

export XILINXD_LICENSE_FILE=/home/liveuser/.xilinx/

/opt/Xilinx/14.7/ISE_DS/settings64.sh

みたいな 環境変数に ライセンスファイルの置き場を指定 そうすると

起動できます。

これで コンソールから ise エンターで 起動できます。

早速起動して uart を いれみます。

https://www.nandland.com/vhdl/modules/module-uart-serial-port-rs232.html

のファイルを あれします。

file ー> newproject で

プロジェクト名を 例えば myuart とかいれます。 ここで どのデバイス使うかとか設定ありますが

とりあえず spartan6 ぐらいいれましょうか 一通りいろいろついてますので

モデルシムつかえるのかな? ちょっとわかっていません。追って考えましょう

ファイル追加して VHDLモジュールを つくります。 最初てきとうに

https://www.nandland.com/vhdl/modules/module-uart-serial-port-rs232.html

にあるように 同じ名前でファイルをつくります。 送受信の箱をつくって

そのしたに階層構造で このページのデモをつくってみます。

コンポーネントという形で 下層においていきます。

entiry なんちゃら is

なのですが

componet に is はつきません これ面倒です。

最上位まだ書いていませんが コンポーネントをこんな感じにおいていきます。

entity uart is

end uart;

architecture RTL of UART_TX is

component UART_TX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_TX_DV : in std_logic;

i_TX_Byte : in std_logic_vector(7 downto 0);

o_TX_Active : out std_logic;

o_TX_Serial : out std_logic;

o_TX_Done : out std_logic

);

end component ;

component UART_RX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_RX_Serial : in std_logic;

o_RX_DV : out std_logic;

o_RX_Byte : out std_logic_vector(7 downto 0)

);

end component ;

begin

end Behavioral;

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10535549

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック