2021年02月13日

【VHDL入門】UARTを実装してみる。シミュレーターまで

https://www.nandland.com/vhdl/modules/module-uart-serial-port-rs232.html

を勝手に借りるとして

ここに コンポーネントとして くっつけるのだ。

entityをコピーして コンポーネントにして貼り付ける。

試してみよう

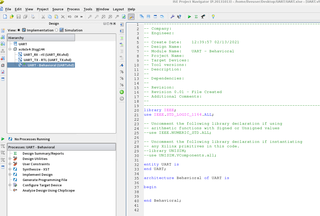

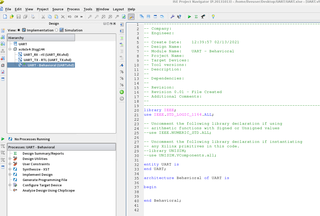

送信と受信があるので これを 1個のUART というファイルで 管理する。

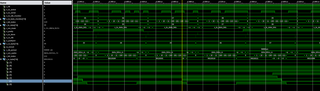

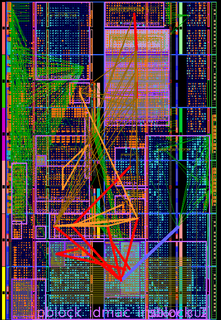

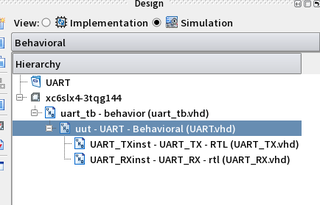

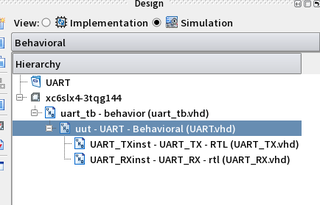

さて それぞれの TX RXは 単純に元々のものをコピーしてきただけなので 階層としては

ここまでいいでしょうか 絵柄はさらに上にシミュ用の あれがなにしてます。

シミュレーター用は VHDL TB テストベンチの略でしょうけどこれでつくります。

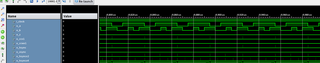

作ったテストベンチは こんな感じ

16進数で 送信に突っ込んで スタートして 送信されたデータを クロックで遅らせて

受信に返します。 この結果がデコードできればいいわけです。

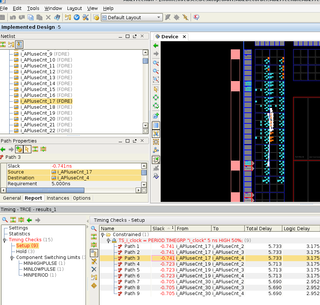

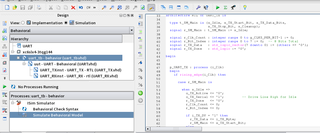

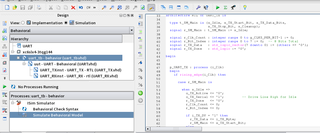

この絵のなかの SimulateBehavioralModel というところをクリックすると なんとまぁ

ということです TBをえらんで居る状態です ここで クリックすると

さあ これで VHDLを書いた テストベンチを書いた シミュレーター起動した

という一連の流れの説明を終了します。

お疲れ様でした。

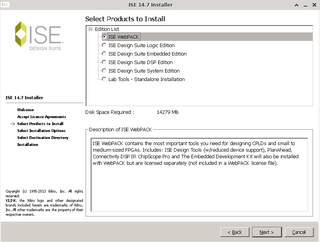

ちなみに私は アルテラ 派です なんで ザイリンクスISEやねん という話ですが

実はー VHDLシミュレーターの起動は こっちが 速いのです。

楽 だから プリミティブが アルテラ出ない場合は こっちで ちゃっちゃと シミュレーターです。

を勝手に借りるとして

ここに コンポーネントとして くっつけるのだ。

entityをコピーして コンポーネントにして貼り付ける。

試してみよう

送信と受信があるので これを 1個のUART というファイルで 管理する。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity UART is

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_TX_DV : in std_logic;

i_TX_Byte : in std_logic_vector(7 downto 0);

o_TX_Active : out std_logic;

o_TX_Serial : out std_logic;

o_TX_Done : out std_logic;

i_RX_Serial : in std_logic;

o_RX_DV : out std_logic;

o_RX_Byte : out std_logic_vector(7 downto 0)

);

end UART;

architecture Behavioral of UART is

component UART_TX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_TX_DV : in std_logic;

i_TX_Byte : in std_logic_vector(7 downto 0);

o_TX_Active : out std_logic;

o_TX_Serial : out std_logic;

o_TX_Done : out std_logic

);

end component;

component UART_RX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_RX_Serial : in std_logic;

o_RX_DV : out std_logic;

o_RX_Byte : out std_logic_vector(7 downto 0)

);

end component;

begin

UART_TXinst : UART_TX generic map (20)

port map (i_Clk, i_TX_DV, i_TX_Byte,o_TX_Active,o_TX_Serial,o_TX_Done);

UART_RXinst : UART_RX generic map (20)

port map (i_Clk, i_RX_Serial,o_RX_DV,o_RX_Byte);

end Behavioral;

さて それぞれの TX RXは 単純に元々のものをコピーしてきただけなので 階層としては

ここまでいいでしょうか 絵柄はさらに上にシミュ用の あれがなにしてます。

シミュレーター用は VHDL TB テストベンチの略でしょうけどこれでつくります。

作ったテストベンチは こんな感じ

16進数で 送信に突っ込んで スタートして 送信されたデータを クロックで遅らせて

受信に返します。 この結果がデコードできればいいわけです。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity UART is

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_TX_DV : in std_logic;

i_TX_Byte : in std_logic_vector(7 downto 0);

o_TX_Active : out std_logic;

o_TX_Serial : out std_logic;

o_TX_Done : out std_logic;

i_RX_Serial : in std_logic;

o_RX_DV : out std_logic;

o_RX_Byte : out std_logic_vector(7 downto 0)

);

end UART;

architecture Behavioral of UART is

component UART_TX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_TX_DV : in std_logic;

i_TX_Byte : in std_logic_vector(7 downto 0);

o_TX_Active : out std_logic;

o_TX_Serial : out std_logic;

o_TX_Done : out std_logic

);

end component;

component UART_RX

generic (

g_CLKS_PER_BIT : integer := 115 -- Needs to be set correctly

);

port (

i_Clk : in std_logic;

i_RX_Serial : in std_logic;

o_RX_DV : out std_logic;

o_RX_Byte : out std_logic_vector(7 downto 0)

);

end component;

begin

UART_TXinst : UART_TX generic map (20)

port map (i_Clk, i_TX_DV, i_TX_Byte,o_TX_Active,o_TX_Serial,o_TX_Done);

UART_RXinst : UART_RX generic map (20)

port map (i_Clk, i_RX_Serial,o_RX_DV,o_RX_Byte);

end Behavioral;

特に怪説いらないと 思いますが

プロセスという形式で クロックをつくって

クロックのエッジで 送信からでた シリアル信号を 1クロック遅らせて 受信にいれます。

今回

UART_TXinst : UART_TX generic map (20)

port map (i_Clk, i_TX_DV, i_TX_Byte,o_TX_Active,o_TX_Serial,o_TX_Done);

UART_RXinst : UART_RX generic map (20)

port map (i_Clk, i_RX_Serial,o_RX_DV,o_RX_Byte);

非同期のクロックを20クロックでという ことにしたので

たとえば クロックが20MHzなら 1Mビット が一秒に転送されます。

では ここでシミュレーターを起動してみましょう。

TBとしてさっきのファイルが追加されているので シミュレーターがクリックすれば起動します。

この絵のなかの SimulateBehavioralModel というところをクリックすると なんとまぁ

ということです TBをえらんで居る状態です ここで クリックすると

さあ これで VHDLを書いた テストベンチを書いた シミュレーター起動した

という一連の流れの説明を終了します。

お疲れ様でした。

ちなみに私は アルテラ 派です なんで ザイリンクスISEやねん という話ですが

実はー VHDLシミュレーターの起動は こっちが 速いのです。

楽 だから プリミティブが アルテラ出ない場合は こっちで ちゃっちゃと シミュレーターです。

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10536230

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック