2021年02月14日

【VHDL入門】20分周のVHDLから シミュレーションまで

おまちかね (だれがじゃ) 単純にクロックを分周して パルスを出す回路だ。

デューティ50%と 20回に一回 1クロックパルスだす両方だ。

あんまりデューティ50%は必要がないのだが 出してみたというだけ 芸のない回路だ。

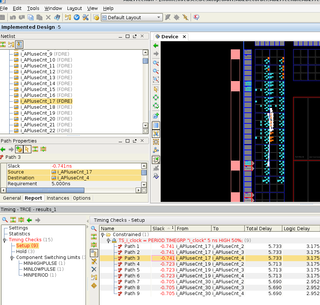

FPGAのなかで 50%デューティのパルスを作ってグローバルクロックに載せてるのを見たことがあるが

あれは 管理しにくいし 遅延がおきるので 扱いにくい

元クロックとは 遅延分ずーっとずれたままになる。

だめだとはいわないけど 私は そんなの管理できないので ・・・

また 配線が複数になるのを防ぐために 回路からは 作られたパルスを 1クロック遅らせて アウトピンにつなぐ これで アンド オア 論理がだらだら 長距離ひっぱれるのを防ぐのだ。

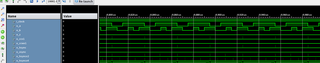

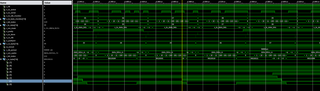

シミュレーションは 20分周なんて10進数なので デシマルでカウンターは表示した。

リセットしてないという苦情も 受け付けなくはないが FPGAって基本RAM動作 コンフィグ終了したところで 普通はカウンター値もゼロとなっている。 そんなデバイス特性をつかった プログラムだ

非同期リセットもできるのだが 非同期なので リセットの瞬間 ひげがでたりするので 私はそれはきらってる。

signal R_div : std_logic:='0'; な書き方で 初期値ゼロになるの もしこれを signal R_div : std_logic:='1'

とかくとコンフィグされたとき1になるらしい。 シミュレーションのときもこれいれてないとリセットでもしないかぎり アンデファインド になるので シムできない しむしむ するには初期値がいるよってこと

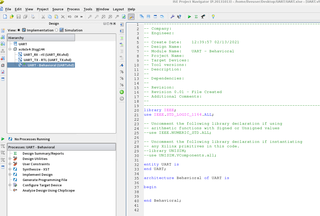

テストベンチはこんなもの

ソースファイルはこんなもの 1クロック遅らせて出力してるのが 設計上負担がない

以上ですーーー

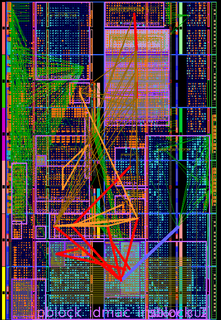

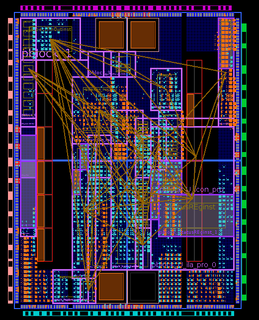

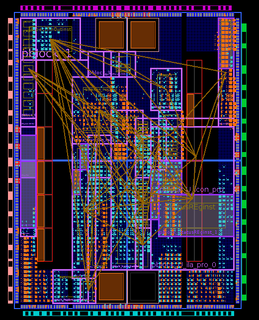

おまけ むかし スパルタン3で200MHz 動作させたときの 配置配線です。

手動で配置しないと なかなか全体として100Mhzで動作させるのは面倒です。

ジョークなのですが 250Mhzで動くかな とやってみたところ 動きはしましたが

FPGAが少々熱くなるので 200Mhzに戻したときのものです。 レポートでは動かないことになっていました。

アルテラで言うと サイクロン なんかも 200Mhzぐらいで動かせればいいな 100Mhzは軽く動作するようです。

デューティ50%と 20回に一回 1クロックパルスだす両方だ。

あんまりデューティ50%は必要がないのだが 出してみたというだけ 芸のない回路だ。

FPGAのなかで 50%デューティのパルスを作ってグローバルクロックに載せてるのを見たことがあるが

あれは 管理しにくいし 遅延がおきるので 扱いにくい

元クロックとは 遅延分ずーっとずれたままになる。

だめだとはいわないけど 私は そんなの管理できないので ・・・

また 配線が複数になるのを防ぐために 回路からは 作られたパルスを 1クロック遅らせて アウトピンにつなぐ これで アンド オア 論理がだらだら 長距離ひっぱれるのを防ぐのだ。

シミュレーションは 20分周なんて10進数なので デシマルでカウンターは表示した。

リセットしてないという苦情も 受け付けなくはないが FPGAって基本RAM動作 コンフィグ終了したところで 普通はカウンター値もゼロとなっている。 そんなデバイス特性をつかった プログラムだ

非同期リセットもできるのだが 非同期なので リセットの瞬間 ひげがでたりするので 私はそれはきらってる。

signal R_div : std_logic:='0'; な書き方で 初期値ゼロになるの もしこれを signal R_div : std_logic:='1'

とかくとコンフィグされたとき1になるらしい。 シミュレーションのときもこれいれてないとリセットでもしないかぎり アンデファインド になるので シムできない しむしむ するには初期値がいるよってこと

テストベンチはこんなもの

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_div IS

END tb_div;

ARCHITECTURE behavior OF tb_div IS

COMPONENT div

PORT(

i_clk : IN std_logic;

o_div_duty50 : out STD_LOGIC;

o_div : OUT std_logic

);

END COMPONENT;

--Inputs

signal i_clk : std_logic := '0';

--Outputs

signal o_div : std_logic;

signal o_div_duty50 : std_logic;

-- Clock period definitions

constant i_clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: div PORT MAP (

i_clk => i_clk,

o_div_duty50 => o_div_duty50,

o_div => o_div

);

-- Clock process definitions

i_clk_process :process

begin

i_clk <= '0';

wait for i_clk_period/2;

i_clk <= '1';

wait for i_clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

wait for i_clk_period*10;

-- insert stimulus here

wait;

end process;

END;

ソースファイルはこんなもの 1クロック遅らせて出力してるのが 設計上負担がない

library ieee;

use ieee.std_logic_1164.all;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

library unisim;

use unisim.vcomponents.all;

entity div is

Port ( i_clk : in STD_LOGIC;

o_div_duty50 : out STD_LOGIC:='0';

o_div : out STD_LOGIC:='0'

);

end div;

architecture Behavioral of div is

signal cnt : std_logic_vector(7 downto 0) := (others => '0');

signal R_div : std_logic:='0';

signal R_div_duty50 : std_logic:='0';

begin

process (i_Clk)

begin

if rising_edge(i_Clk) then

cnt <=cnt + '1';

if(cnt=X"09")then

R_div_duty50<='0';

elsif(cnt=X"13")then

R_div_duty50<='1';

cnt<=(others => '0');

R_div<='1';

else

R_div<='0';

end if;

o_div_duty50<=R_div_duty50;

o_div<=R_div;

end if;

end process;

end Behavioral;

以上ですーーー

おまけ むかし スパルタン3で200MHz 動作させたときの 配置配線です。

手動で配置しないと なかなか全体として100Mhzで動作させるのは面倒です。

ジョークなのですが 250Mhzで動くかな とやってみたところ 動きはしましたが

FPGAが少々熱くなるので 200Mhzに戻したときのものです。 レポートでは動かないことになっていました。

アルテラで言うと サイクロン なんかも 200Mhzぐらいで動かせればいいな 100Mhzは軽く動作するようです。

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10537958

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック