2021年02月26日

【VHDL入門】ABZ信号から Hsync Vsyncを作り出してみよう その1

【VHDL入門】辛口かな ABZ信号から Hsync Vsyncを作り出してみよう

ABZ が ABZである所以は 逆回転をキャンセルできることにある。

ロータリーエンコーダーはバックラッシュ起こすことがある。

ぷるぷると震えると あれでなにで Hsyncにしたとき Hsyncが 余分に?

出てしまいます。 ではどうすればいいでしょうか とりあえず 単純にデコードしてみましょう。

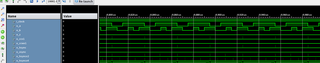

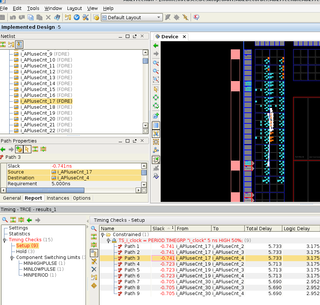

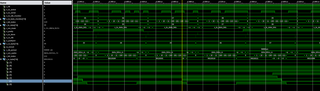

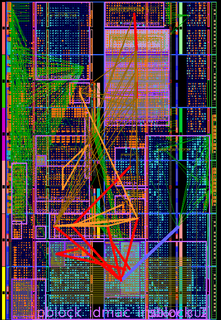

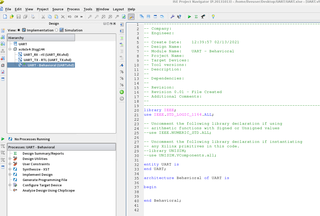

さっき作ったフリーランと デコーダーを合成します。

CCだけを Hsyncとしてみます。

CCW逆回転も ORして Hsyncにいまのところだらしなく どっち周りでも Hsyncします。

さてこれから 面倒です バックラッシュでは Hsyncを出さないように改造していくことにしましょう

しかし 本日はここまで

ABZ が ABZである所以は 逆回転をキャンセルできることにある。

ロータリーエンコーダーはバックラッシュ起こすことがある。

ぷるぷると震えると あれでなにで Hsyncにしたとき Hsyncが 余分に?

出てしまいます。 ではどうすればいいでしょうか とりあえず 単純にデコードしてみましょう。

さっき作ったフリーランと デコーダーを合成します。

CCだけを Hsyncとしてみます。

CCW逆回転も ORして Hsyncにいまのところだらしなく どっち周りでも Hsyncします。

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 01:52:08 02/26/2021

-- Design Name:

-- Module Name: ABz2HsyncVsync - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library IEEE;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity ABz2HsyncVsync is

port (

I_Clock :in std_logic;

o_A :out std_logic:='0';-- 10khz

o_B :out std_logic:='0';

o_Z :out std_logic:='0';

O_CCx1 :out std_logic:='0';

O_CCWx1 :out std_logic:='0';

o_Hsync :out std_logic:='0';

o_Vsync :out std_logic:='0'

);

end ABz2HsyncVsync;

architecture Behavioral of ABz2HsyncVsync is

component AbzFreeRun is

Port ( i_clock : in STD_LOGIC;o_A:out std_logic:='0';o_B:out std_logic:='0';o_Z:out std_logic:='0');

end component;

component AB2CC_CCW

port (i_Clock: in std_logic;i_A_n,i_B_n: in std_logic;O_CCx1: out std_logic;O_CCWx1: out std_logic;O_iA_Alive: out std_logic;O_iB_Alive: out std_logic);

end component;

signal w_A :std_logic;

signal w_B :std_logic;

signal w_Z :std_logic;

signal w_CCx1 :std_logic;

signal w_CCWx1 :std_logic;

signal w_Hsync :std_logic;

signal w_Vsync :std_logic;

begin

AbzFreeRuninst: AbzFreeRun

Port map( i_clock =>I_Clock,

o_A =>w_A,

o_B =>w_B,

o_Z =>w_Z

);

AB2CC_CCWinst: AB2CC_CCW

port map(

i_Clock =>I_Clock,

i_A_n =>w_A,

i_B_n =>w_B,

O_CCx1 =>w_CCx1,

O_CCWx1 =>w_CCWx1,

O_iA_Alive =>open,

O_iB_Alive =>open

);

o_A <=w_A;

o_B <=w_B;

o_Z <=w_Z;

O_CCx1 <=w_CCx1;

O_CCWx1 <=w_CCWx1;

Zsync :process (i_clock)

begin

if rising_edge(i_clock) then

w_Hsync <=w_CCx1 or w_CCx1;

w_Vsync <=(w_CCx1 or w_CCx1) and w_Z;

o_Hsync <=w_Hsync;--このコンポーネントからの出力はレジスタ出力とする

o_Vsync <=w_Vsync;--このコンポーネントからの出力はレジスタ出力とする

end if;

end process ;

end Behavioral;

library IEEE;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity AB2CC_CCW is-------------------------ɗ̓Zbg͎gȂ |C@ōs

port (

i_Clock : in std_logic;

i_A_n,i_B_n : in std_logic;------------FPGA ̓tHgJvŎM ڑ gŒ

O_CCx1 : out std_logic;

O_CCWx1 : out std_logic;

O_iA_Alive : out std_logic;

O_iB_Alive : out std_logic

);

end AB2CC_CCW;

architecture behavioral of AB2CC_CCW is

signal R_A_DL,R_B_DL : std_logic_vector(2 downto 0);

signal A_RiseEdji,A_FallEdji : std_logic:='0';

signal B_RiseEdji,B_FallEdji : std_logic:='0';

signal R_CCx1,R_CCx2,R_CCx4 : std_logic:='0';

signal R_CCWx1,R_CCWx2,R_CCWx4 : std_logic:='0';

signal R_CNT_B : std_logic_vector( 3 downto 0):="0000";

signal R_CNT_A : std_logic_vector( 3 downto 0):="0000";

signal R_CNT_B_UP : std_logic:='0';

signal R_CNT_A_UP : std_logic:='0';

signal w_Alive_B : std_logic:='0';

signal w_Alive_A : std_logic:='0';

signal w_Fltd_A_n : std_logic:='0';

signal w_Fltd_B_n : std_logic:='0';

component Filter

port (

I_Clock : in std_logic;

i_Enable: in std_logic;

I_Din : in std_logic;

O_Dout : out std_logic

);

end component;

component FreeRun

port (

I_Clock : in std_logic;

O_Dout : out std_logic

);

end component;

signal w_FreeRunTMUP : std_logic;

constant HIGH : std_logic:='1';

begin

FilterA_inst : Filter port map(I_Clock=>i_Clock,i_Enable=>HIGH,I_Din =>i_A_n,O_Dout => w_Fltd_A_n);

FilterB_inst : Filter port map(I_Clock=>i_Clock,i_Enable=>HIGH,I_Din =>i_B_n,O_Dout => w_Fltd_B_n);

FreeRun_inst : FreeRun port map(I_Clock=>i_Clock,O_Dout =>w_FreeRunTMUP );

DetectA_inst : Filter port map(I_Clock=>i_Clock,i_Enable=>w_FreeRunTMUP,I_Din =>R_CNT_A_UP,O_Dout => w_Alive_A);

DetectB_inst : Filter port map(I_Clock=>i_Clock,i_Enable=>w_FreeRunTMUP,I_Din =>R_CNT_B_UP,O_Dout => w_Alive_B);

process (i_Clock)

begin

if(i_Clock'event and i_Clock = '1') then

O_iA_Alive<=w_Alive_A;

O_iB_Alive<=w_Alive_B;

if w_FreeRunTMUP = '1' then

R_CNT_A <=(others =>'0');

R_CNT_B <=(others =>'0');

else

if R_CNT_A =X"F" then

R_CNT_A <=R_CNT_A;

R_CNT_A_UP <='1';

else

if A_RiseEdji = '1' or A_FallEdji ='1' then-----------------pX邱

R_CNT_A <=R_CNT_A + '1';

end if;

R_CNT_A_UP <='0';

end if;

if R_CNT_B =X"F" then

R_CNT_B <=R_CNT_B;

R_CNT_B_UP <='1';

else

if B_RiseEdji = '1' or B_FallEdji ='1' then-----------------pX邱

R_CNT_B <=R_CNT_B + '1';

end if;

R_CNT_B_UP <='0';

end if;

end if;

end if;

end process;

process (i_Clock)

begin

if(i_Clock'event and i_Clock = '1') then

R_A_DL <= R_A_DL(1 downto 0) & not w_Fltd_A_n;

R_B_DL <= R_B_DL(1 downto 0) & not w_Fltd_B_n;

A_RiseEdji <= R_A_DL(1) and (not R_A_DL(2)) ;

A_FallEdji <= not R_A_DL(1) and R_A_DL(2) ;

B_RiseEdji <= R_B_DL(1) and (not R_B_DL(2)) ;

B_FallEdji <= not R_B_DL(1) and R_B_DL(2) ;

R_CCx1 <= A_RiseEdji and (not R_B_DL(0));

R_CCWx1 <= A_FallEdji and (not R_B_DL(0));

O_CCx1 <=R_CCx1;

O_CCWx1 <=R_CCWx1;

end if;

end process;

end Behavioral;

さてこれから 面倒です バックラッシュでは Hsyncを出さないように改造していくことにしましょう

しかし 本日はここまで

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10563541

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック