2021年02月26日

【VHDL入門】速度比較 エンコーダーABZ相 ソースファイル付き

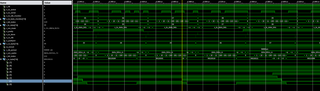

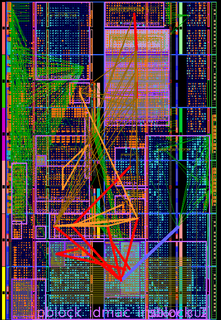

前回200Mhzで動作できるかみたいな スパルタン3E

だから スパルタン6では どうかなと

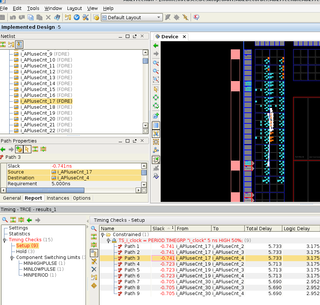

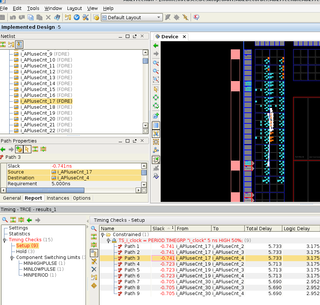

結果は スパルタン3E 160Mhz動作OK ^^;

スパルタン6 280Mhz動作OK らしい ^^;

周期5Nではだめってさ

スパルタン6では 3nSでもOKだそうだ えっ 300Mhzで動作できるの?ってさ

だから スパルタン6では どうかなと

結果は スパルタン3E 160Mhz動作OK ^^;

スパルタン6 280Mhz動作OK らしい ^^;

周期5Nではだめってさ

スパルタン6では 3nSでもOKだそうだ えっ 300Mhzで動作できるの?ってさ

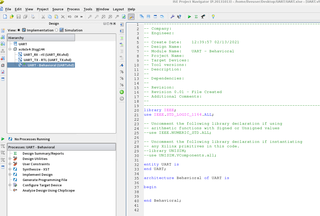

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.numeric_std.all;

entity AbzFreeRun is

Port ( i_clock : in STD_LOGIC;--20Mhz

o_A :out std_logic:='0';-- 10khz

o_B :out std_logic:='0';

o_Z :out std_logic:='0'

);

end AbzFreeRun;

architecture Behavioral of AbzFreeRun is

type t_SM_Main is (Aup, Bup,ADown,BDown);

signal r_SM_Main : t_SM_Main := Aup;

signal B_StatUpdate : Boolean:=false;

signal Z_Flg : Boolean:=false;

signal i_StatUpdatecnt: integer:=0;

signal i_APluseCnt : integer:=0;

begin

ZtimgProcess :process (i_clock)

begin

if rising_edge(i_clock) then

if(B_StatUpdate) and r_SM_Main= Aup then

if(i_APluseCnt=36-1) then

i_APluseCnt <=0;

Z_Flg <= true;

else

i_APluseCnt <= i_APluseCnt +1;

Z_Flg <= false;

end if;

end if;

end if;

end process ;

process (i_clock)

begin

if rising_edge(i_clock) then

if(i_StatUpdatecnt=500-1) then

i_StatUpdatecnt <=0;

B_StatUpdate <= true;

else

i_StatUpdatecnt <= i_StatUpdatecnt +1;

B_StatUpdate <= false;

end if;

end if;

end process ;

abz_inst:process (i_clock)

begin

if rising_edge(i_clock) then

if(B_StatUpdate ) then

case r_SM_Main is

when Aup =>r_SM_Main<=Bup;o_A<='1';

if(Z_Flg) then o_Z <='1';else o_Z <='0'; end if;

when Bup =>r_SM_Main<=ADown;o_B<='1';

when ADown =>r_SM_Main<=BDown;o_A<='0';

when BDown =>r_SM_Main<=Aup;o_B<='0';

when others =>r_SM_Main<=Aup;

end case;

end if;

end if;

end process ;

end Behavioral;

この記事へのコメント

コメントを書く

この記事へのトラックバックURL

https://fanblogs.jp/tb/10563428

※ブログオーナーが承認したトラックバックのみ表示されます。

この記事へのトラックバック